addressing. Some architectures, including that of the Pentium, have a collection of two or more specialized sets (such as data and displacement). One advantage of this latter approach is that, for a fixed number of registers, a functional split requires fewer bits to be used in the instruction. For example, with two sets of eight registers, only 3 bits are required to identify a register; the opcode implicitly will determine which set of registers is being referenced.

- Address range: For addresses that reference memory, the range of addresses that can be referenced is related to the number of address bits. Because this imposes a severe limitation, direct addressing is rarely used. With displacement addressing, the range is opened up to the length of the address register. Even so, it is still convenient to allow rather large displacements from the register address, which requires a relatively large number of address bits in the instruction.

- Address granularity: For addresses that reference memory rather than registers, another factor is the granularity of addressing. In a system with 16- or 32-bit words, an address can reference a word or a byte at the designer's choice. Byte addressing is convenient for character manipulation but requires, for a fixed-size memory, more address bits.

Thus, the designer is faced with a host of factors to consider and balance. How critical the various choices are is not clear. As an example, we cite one study [CRAG79] that compared various instruction format approaches, including the use of a stack, general-purpose registers, an accumulator, and only memory-to-register approaches. Using a consistent set of assumptions, no significant difference in code space or execution time was observed.

Let us briefly look at how two historical machine designs balance these various factors.

PDP-8 One of the simplest instruction designs for a general-purpose computer was for the PDP-8 [BELL78b]. The PDP-8 uses 12-bit instructions and operates on 12-bit words. There is a single general-purpose register, the accumulator.

Despite the limitations of this design, the addressing is quite flexible. Each memory reference consists of 7 bits plus two 1-bit modifiers. The memory is divided into fixed-length pages of  $2^7 = 128$  words each. Address calculation is based on references to page 0 or the current page (page containing this instruction) as determined by the page bit. The second modifier bit indicates whether direct or indirect addressing is to be used. These two modes can be used in combination, so that an indirect address is a 12-bit address contained in a word of page 0 or the current page. In addition, 8 dedicated words on page 0 are autoindex "registers." When an indirect reference is made to one of these locations, preindexing occurs.

Figure 11.4 shows the PDP-8 instruction format. There are a 3-bit opcode and three types of instructions. For opcodes 0 through 5, the format is a single-address memory reference instruction including a page bit and an indirect bit. Thus, there are only six basic operations. To enlarge the group of operations, opcode 7 defines a register reference or microinstruction. In this format, the remaining bits are used to encode additional operations. In general, each bit defines a specific operation (e.g., clear accumulator), and these bits can be combined in a single instruction. The microinstruction strategy was used as far back as the PDP-1 by DEC and is, in a sense, a forerunner of

|                                                                                                                                                                                                                                     |            |         |      |     |     | Men   | nory Re                                                                                                                                                                                                                                                           | ference | Instruc | tions  |     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--------|-----|--|

| 5 B 1 5 1 5 1 1 1                                                                                                                                                                                                                   | Opcode     |         | D/I  | Z/C |     | . ,   | Di                                                                                                                                                                                                                                                                | splacem | ent     |        |     |  |

| 0                                                                                                                                                                                                                                   |            | 2       | 3    | 4   | 5   |       |                                                                                                                                                                                                                                                                   |         |         |        | 11  |  |

|                                                                                                                                                                                                                                     |            |         |      |     |     | Input | /Output                                                                                                                                                                                                                                                           | Instru  | ctions  |        |     |  |

| 1.                                                                                                                                                                                                                                  | 1          | 0       |      |     | Dev | vice  |                                                                                                                                                                                                                                                                   | •       |         | Opcode |     |  |

| 0                                                                                                                                                                                                                                   |            | 2       | 3    |     |     |       |                                                                                                                                                                                                                                                                   | 8       | 9       |        | 11  |  |

| Group 1 microinstructions  Register Reference Instructions                                                                                                                                                                          |            |         |      |     |     |       |                                                                                                                                                                                                                                                                   |         |         |        |     |  |

| 1                                                                                                                                                                                                                                   | 1          | 1       | 0    | CLA | CLL | CMA   | CML                                                                                                                                                                                                                                                               | RAR     | RAL     | BSW    | IAC |  |

| 0                                                                                                                                                                                                                                   | 1          | 2       | 3    | 4   | 5   | 6     | 7                                                                                                                                                                                                                                                                 | 8       | 9       | 10     | 11  |  |

| Group 2 microinstructions                                                                                                                                                                                                           |            |         |      |     |     |       |                                                                                                                                                                                                                                                                   |         |         |        |     |  |

| 1                                                                                                                                                                                                                                   | 1          | 1       | 0    | CLA | SMA | SZA   | SNL                                                                                                                                                                                                                                                               | RSS     | OSR     | HLT    | 0   |  |

| 0                                                                                                                                                                                                                                   | 1          | 2       | 3    | 4   | 5   | 6     | 7                                                                                                                                                                                                                                                                 | 8       | 9       | 10     | 11  |  |

| Grou                                                                                                                                                                                                                                | ıp 3 micro | instruc | ions |     |     |       |                                                                                                                                                                                                                                                                   |         |         |        |     |  |

| 11.                                                                                                                                                                                                                                 | 1.1.       | 101     | 0    | CLA | MQA | 0     | MQL                                                                                                                                                                                                                                                               | 0       | 0       | 0      | 1   |  |

| 0                                                                                                                                                                                                                                   | 1          | 2       | 3    | 4   | 5   | 6     | 7                                                                                                                                                                                                                                                                 | 8       | 9       | 10     | 11  |  |

| D/I = Direct/Indirect address Z/C = Page 0 or Current page CLA = Clear Accumulator CLL = Clear Link CMA = CoMplement Accumulator CML = CoMplement Link RAR = Rotate Accumulator Right RAL = Rotate Accumulator Left BSW = Byte SWap |            |         |      |     |     |       | IAC = Increment ACcumulator SMA = Skip on Minus Accumulator SZA = Skip on Zero Accumulator SNL = Skip on Nonzero Link RSS = Reverse Skip Sense OSR = Or with Switch Register HLT = HaLT MQA = Multiplier Quotient into Accumulator MQL = Multiplier Quotient Load |         |         |        |     |  |

Figure 11.4 PDP-8 Instruction Formats

today's microprogrammed machines, to be discussed in Part Four. Opcode 6 is the I/O operation; 6 bits are used to select one of 64 devices, and 3 bits specify a particular I/O command.

The PDP-8 instruction format is remarkably efficient. It supports indirect addressing, displacement addressing, and indexing. With the use of the opcode extension, it supports a total of approximately 35 instructions. Given the constraints of a 12-bit instruction length, the designers could hardly have done better.

PDP-10 A sharp contrast to the instruction set of the PDP-8 is that of the PDP-10. The PDP-10 was designed to be a large-scale time-shared system, with an emphasis on making the system easy to program, even if additional hardware expense was involved.

Among the design principles that were employed in designing the instruction set were [BELL78c].

- Orthogonality: Orthogonality is a principle by which two variables are independent of each other. In the context of an instruction set, the term indicates that other elements of an instruction are independent of (not determined by) the opcode. The PDP-10 designers use the term to describe the fact that an address is always computed in the same way, independent of the opcode. This is in contrast to many machines, where the address mode sometimes depends implicitly on the operator being used.

- Completeness: Each arithmetic data type (integer, fixed-point, real) should have a complete and identical set of operations.

Figure 11.5 PDP-10 Instruction Format

Direct addressing: Base plus displacement addressing, which places a memory organization burden on the programmer, was avoided in favor of direct addressing.

Each of these principles advances the main goal of ease of programming.

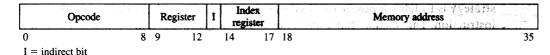

The PDP-10 has a 36-bit word length and a 36-bit instruction length. The fixed instruction format is shown in Figure 11.5. The opcode occupies 9 bits, allowing up to 512 operations. In fact, a total of 365 different instructions are defined. Most instructions have two addresses, one of which is one of 16 general-purpose registers. Thus, this operand reference occupies 4 bits. The other operand reference starts with an 18-bit memory address field. This can be used as an immediate operand or a memory address. In the latter usage, both indexing and indirect addressing are allowed. The same general-purpose registers are also used as index registers.

A 36-bit instruction length is true luxury. There is no need to do clever things to get more opcodes; a 9-bit opcode field is more than adequate. Addressing is also straightforward. An 18-bit address field makes direct addressing desirable. For memory sizes greater than 2<sup>18</sup>, indirection is provided. For the ease of the programmer, indexing is provided for table manipulation and iterative programs. Also, with an 18-bit operand field, immediate addressing becomes attractive.

The PDP-10 instruction set design does accomplish the objectives listed earlier [LUND77]. It eases the task of the programmer or compiler at the expense of an inefficient utilization of space. This was a conscious choice made by the designers and therefore cannot be faulted as poor design.

## Variable-Length Instructions

The examples we have looked at so far have used a single fixed instruction length, and we have implicitly discussed trade-offs in that context. But the designer may choose instead to provide a variety of instruction formats of different lengths. This tactic makes it easy to provide a large repertoire of opcodes, with different opcode lengths. Addressing can be more flexible, with various combinations of register and memory references plus addressing modes. With variable-length instructions, these many variations can be provided efficiently and compactly.

The principal price to pay for variable-length instructions is an increase in the complexity of the processor. Falling hardware prices, the use of microprogramming (discussed in Part Four), and a general increase in understanding the principles of processor design have all contributed to making this a small price to pay. However, we will see that RISC and superscalar machines can exploit the use of fixed-length instructions to provide improved performance.

The use of variable-length instructions does not remove the desirability of making all of the instruction lengths integrally related to the word length. Because the processor does not know the length of the next instruction to be fetched, a typical

strategy is to fetch a number of bytes or words equal to at least the longest possible instruction. This means that sometimes multiple instructions are fetched. However, as we shall see in Chapter 12, this is a good strategy to follow in any case.

PDP-11 The PDP-11 was designed to provide a powerful and flexible instruction set within the constraints of a 16-bit minicomputer [BELL70].

The PDP-11 employs a set of eight 16-bit general-purpose registers. Two of these registers have additional significance: One is used as a stack pointer for specialpurpose stack operations, and one is used as the program counter, which contains the address of the next instruction.

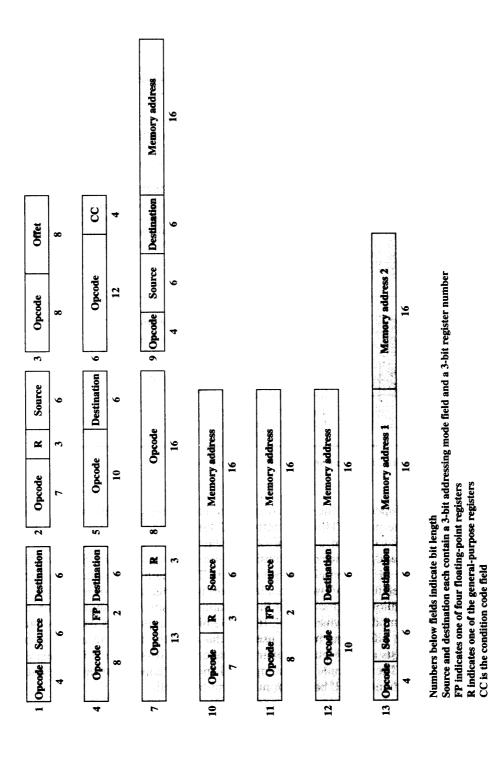

Figure 11.6 shows the PDP-11 instruction formats. Thirteen different formats are used, encompassing zero-, one-, and two-address instruction types. The opcode can vary from 4 to 16 bits in length. Register references are 6 bits in length. Three bits identify the register, and the remaining 3 bits identify the addressing mode. The PDP-11 is endowed with a rich set of addressing modes. One advantage of linking the addressing mode to the operand rather than the opcode, as is sometimes done, is that any addressing mode can be used with any opcode. As was mentioned, this independence is referred to as orthogonality.

PDP-11 instructions are usually one word (16 bits) long. For some instructions. one or two memory addresses are appended, so that 32-bit and 48-bit instructions are part of the repertoire. This provides for further flexibility in addressing.

The PDP-11 instruction set and addressing capability are complex. This increases both hardware cost and programming complexity. The advantage is that more efficient or compact programs can be developed.

VAX Most architectures provide a relatively small number of fixed instruction formats. This can cause two problems for the programmer. First, addressing mode and opcode are not orthogonal. For example, for a given operation, one operand must come from a register and another from memory, or both from registers, and so on. Second, only a limited number of operands can be accommodated: typically up to two or three. Because some operations inherently require more operands, various strategies must be used to achieve the desired result using two or more instructions.

To avoid these problems, two criteria were used in designing the VAX instruction format [STRE78]:

- 1. All instructions should have the "natural" number of operands.

- 2. All operands should have the same generality in specification.

The result is a highly variable instruction format. An instruction consists of a 1- or 2-byte opcode followed by from zero to six operand specifiers, depending on the opcode. The minimal instruction length is 1 byte, and instructions up to 37 bytes can be constructed. Figure 11.7 gives a few examples.

The VAX instruction begins with a 1-byte opcode. This suffices to handle most VAX instructions. However, as there are over 300 different instructions, 8 bits are not enough. The hexadecimal codes FD and FF indicate an extended opcode, with the actual opcode being specified in the second byte.

The remainder of the instruction consists of up to six operand specifiers. An operand specifier is, at minimum, a 1-byte format in which the leftmost 4 bits are the

Figure 11.6 Instruction Formats for the PDP-11

| Hexadecimal<br>Format                  | Explanation                                                                                                                                                           | Assembler Notation and Description                                                                                                             |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 bits 5 5                             | Opcode for RSB                                                                                                                                                        | RSB<br>Return from subroutine                                                                                                                  |

| D 4 5 9                                | Opcode for CLRL<br>Register R9                                                                                                                                        | CLRL R9<br>Clear register R9                                                                                                                   |

| B 0<br>C 4<br>6 4<br>0 1<br>A B<br>1 9 | Opcode for MOVW Word displacement mode, Register R4 356 in hexadecimal Byte displacement mode, Register R11 25 in hexadecimal                                         | MOVW 356(R4), 25(R11)  Move a word from address that is 356 plus contents of R4 to address that is 25 plus contents of R11                     |

| C 1<br>0 5<br>5 0<br>4 2<br>D F        | Opcode for ADDL3 Short literal 5 Register mode R0 Index prefix R2 Indirect word relative (displacement from PC) Amount of displacement from PC relative to location A | ADDL3 #5, R0, @A[R2] Add 5 to a 32-bit integer in R0 and store the result in location whose address is sum of A and 4 times the contents of R2 |

Figure 11.7 Example of VAX Instructions

address mode specifier. The only exception to this rule is the literal mode, which is signaled by the pattern 00 in the leftmost 2 bits, leaving space for a 6-bit literal. Because of this exception, a total of 12 different addressing modes can be specified.

An operand specifier often consists of just one byte, with the rightmost 4 bits specifying one of 16 general-purpose registers. The length of the operand specifier can be extended in one of two ways. First, a constant value of one or more bytes may immediately follow the first byte of the operand specifier. An example of this is the displacement mode, in which an 8-, 16-, or 32-bit displacement is used. Second, an index mode of addressing may be used. In this case, the first byte of the operand specifier consists of the 4-bit addressing mode code of 0100 and a 4-bit index register identifier. The remainder of the operand specifier consists of the base address specifier, which may itself be one or more bytes in length.

The reader may be wondering, as the author did, what kind of instruction requires six operands. Surprisingly, the VAX has a number of such instructions. Consider

This instruction adds two packed decimal numbers. OP1 and OP2 specify the length and starting address of one decimal string; OP3 and OP4 specify a second string. These two strings are added and the result is stored in the decimal string whose length and starting location are specified by OP5 and OP6.

The VAX instruction set provides for a wide variety of operations and addressing modes. This gives a programmer, such as a compiler writer, a very powerful and flexible tool for developing programs. In theory, this should lead to efficient machinelanguage compilations of high-level language programs and, in general, to effective and efficient use of processor resources. The penalty to be paid for these benefits is the increased complexity of the processor compared with a processor with a simpler instruction set and format.

We return to these matters in Chapter 13, where we examine the case for very simple instruction sets.

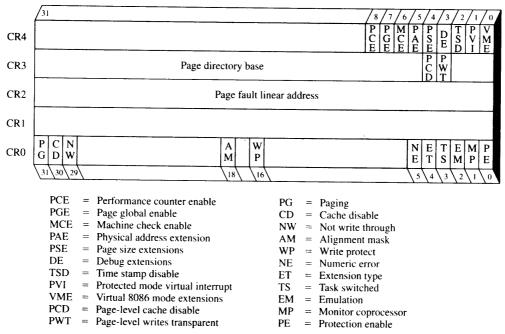

# 11.4 PENTIUM AND POWERPC INSTRUCTION FORMATS

#### **Pentium Instruction Formats**

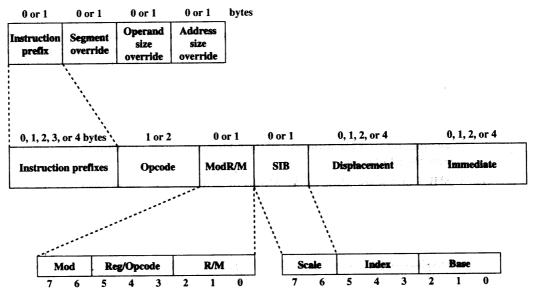

The Pentium is equipped with a variety of instruction formats. Of the elements described in this subsection, only the opcode field is always present. Figure 11.8 illustrates the general instruction format. Instructions are made up of from zero to four optional instruction prefixes, a 1- or 2-byte opcode, an optional address specifier (which consists of the ModR/m byte and the Scale Index byte) an optional displacement, and an optional immediate field.

Figure 11.8 Pentium Instruction Format

Let us first consider the prefix bytes:

- Instruction prefixes: The instruction prefix, if present, consists of the LOCK prefix or one of the repeat prefixes. The LOCK prefix is used to ensure exclusive use of shared memory in multiprocessor environments. The repeat prefixes specify repeated operation of a string, which enables the Pentium to process strings much faster than with a regular software loop. There are five different repeat prefixes: REP, REPE, REPZ, REPNE, and REPNZ. When the absolute REP prefix is present, the operation specified in the instruction is executed repeatedly on successive elements of the string; the number of repetitions is specified in register CX. The conditional REP prefix causes the instruction to repeat until the count in CX goes to zero or until the condition is met.

- Segment override: Explicitly specifies which segment register an instruction should use, overriding the default segment-register selection generated by the Pentium for that instruction.

- Address size: The processor can address memory using either 16- or 32-bit addresses. The address size determines the displacement size in instructions and the size of address offsets generated during effective address calculation. One of these sizes is designated as default, and the address size prefix switches between 32-bit and 16-bit address generation.

- Operand size: An instruction has a default operand size of 16 or 32 bits, and the operand prefix switches between 32-bit and 16-bit operands.

The instruction itself includes the following fields:

- Opcode: One- or two-byte opcode. The opcode may also include bits that specify if data is byte- or full-size (16 or 32 bits depending on context), direction of data operation (to or from memory), and whether an immediate data field must be sign extended.

- ModR/m: This byte, and the next, provide addressing information. The ModR/m byte specifies whether an operand is in a register or in memory; if it is in memory, then fields within the byte specify the addressing mode to be used. The ModR/m byte consists of three fields: The Mod field (2 bits) combines with the r/m field to form 32 possible values: 8 registers and 24 indexing modes; the Reg/Opcode field (3 bits) specifies either a register number or three more bits of opcode information; the r/m field (3 bits) can specify a register as the location of an operand, or it can form part of the addressing-mode encoding in combination with the Mod field.

- SIB: Certain encoding of the ModR/m byte specifies the inclusion of the SIB byte to specify fully the addressing mode. The SIB byte consists of three fields: The Scale field (2 bits) specifies the scale factor for scaled indexing; the Index field (3 bits) specifies the index register; the Base field (3 bits) specifies the base register.

- **Displacement:** When the addressing-mode specifier indicates that a displacement is used, an 8-, 16-, or 32-bit signed integer displacement field is added.

- Immediate: Provides the value of an 8-, 16-, or 32-bit operand.

Several comparisons may be useful here. In the Pentium format, the addressing mode is provided as part of the opcode sequence rather than with each operand. Because only one operand can have address-mode information, only one memory operand can be referenced in an instruction. In contrast, the VAX carries the addressmode information with each operand, allowing memory-to-memory operations. The Pentium instructions are therefore more compact. However, if a memory-to-memory operation is required, the VAX can accomplish this in a single instruction.

The Pentium format allows the use of not only 1-byte, but also 2-byte and 4-byte offsets for indexing. Although the use of the larger index offsets results in longer instructions, this feature provides needed flexibility. For example, it is useful in addressing large arrays or large stack frames. In contrast, the IBM S/370 instruction format allows offsets no greater than 4K bytes (12 bits of offset information), and the offset must be positive. When a location is not in reach of this offset, the compiler must generate extra code to generate the needed address. This problem is especially apparent in dealing with stack frames that have local variables occupying in excess of 4K bytes. As [DEWA90] puts it, "Generating code for the 370 is so painful as a result of that restriction that there have even been compilers for the 370 that simply chose to limit the size of the stack frame to 4K bytes."

As can be seen, the encoding of the Pentium instruction set is very complex. This has to do partly with the need to be backward compatible with the 8086 machine and partly with a desire on the part of the designers to provide every possible assistance to the compiler writer in producing efficient code. It is a matter of some debate whether an instruction set as complex as this is preferable to the opposite extreme of the RISC instruction sets.

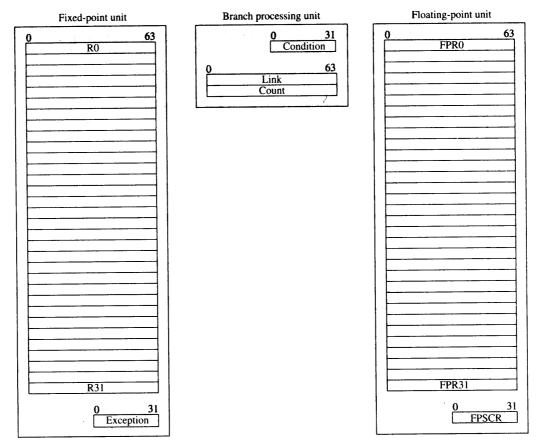

#### PowerPC Instruction Formats

All instructions in the PowerPC are 32 bits long and follow a regular format. The first 6 bits of an instruction specify the operation to be performed. In some cases, there is an extension to the opcode elsewhere in the instruction that specifies a particular subcase of an operation. In Figure 11.9, opcode bits are represented by the shaded portion of each format.

Note the regular structure of the formats, which eases the job of the instruction decode units. For all load/store, arithmetic, and logical instructions, the opcode is followed by two 5-bit register references, enabling 32 general-purpose registers to be used.

The branch instructions include a link (L) bit that indicates that the effective address of the instruction following the branch instruction is to be placed in the link register. Two forms of the instruction also include a bit (A) that indicates whether the addressing mode is absolute or PC relative. For the conditional branch instructions, the CR bit field specifies the bit to be tested in the condition register. The options field specifies the conditions under which the branch is to be taken. The following conditions may be specified:

- · Branch always.

- Branch if count  $\neq 0$  and condition is false.

- Branch if count  $\neq 0$  and condition is true.

- Branch if count = 0 and condition is false.

# **410** CHAPTER 11 / INSTRUCTION SETS: ADDRESSING MODES AND FORMATS

| ← 6 Bits ←     | ← 5 Bits | <b>←</b> 5 Bits — | 16 Bits ———                         |      | <b>-</b> |

|----------------|----------|-------------------|-------------------------------------|------|----------|

| Branch         | n-       | Lor               | g immediate                         | A    | L        |

| Br Conditional | Options  | CR bit            | Branch displacement                 | A    | L        |

| Br Conditional | Options  | CR bit            | Indirect through Link or Count Regi | ster | L        |

#### (a) Branch instructions

| CR | Dest bit | Source bit | Source bit | Add, or, Xor, etc. / | ٦ |

|----|----------|------------|------------|----------------------|---|

#### (b) Condition register logical instructions

| Ld/st Idire | ct Dest register | Base register | <del></del>    |                    |   |   |

|-------------|------------------|---------------|----------------|--------------------|---|---|

| Ld/st Idire | ct Dest register | Base register | Index register | Size, sign, update | / | 7 |

| Ld/st Idire | ct Dest register | Base register | Disp           | хо                 | k |   |

# (c) Load/store instructions

| Arithmetic      | Dest register | Src register  | Src register | o    | Add,                | sub, etc. |   | R |

|-----------------|---------------|---------------|--------------|------|---------------------|-----------|---|---|

| Add, Sub, etc.  | Dest register | Src register  | Sig          | ned  | immediate           | value     |   |   |

| Logical         | Src register  | Dest register | Src register | Γ    | Add, Or,            | Xor, etc. |   | R |

| And, Or, etc.   | Src register  | Dest register | Uns          | igne | d immediat          | e value   |   |   |

| Rotate          | Src register  | Dest register | Shift amt    | Ma   | Mask begin Mask end |           |   | R |

| Rotate or shift | Src register  | Dest register | Src register |      | Shift type          | or mask   | - | R |

| Rotate          | Src register  | Dest register | Shift amt    |      | Mask                | хо        | s | R |

| Rotate          | Src register  | Dest register | Src register |      | Mask                | хо        |   | R |

| Shift           | Src register  | Dest register | Shift amt    | 9    | Shift type or Mask  |           | s | R |

(d) Integer arithmetic, logical, and shift/rotate instructions

| Flt sgl / dbl | Dest Register | Src Register |              |              |           |   |  |

|---------------|---------------|--------------|--------------|--------------|-----------|---|--|

|               |               |              | Src Register | Src Register | Fadd, ec. | R |  |

(e) Floating-point arithmetic instructions

A = Absolute or PC Relative \* = 64-bit implementation only

L = Link to Subroutine

O = Record Overflow in XER

R = Record Conditions in CR1

XO = OPCode Extension

S = Part of Shift Amount Field

Figure 11.9 PowerPC Instruction Formats

- Branch if count = 0 and condition is true.

- Branch if count  $\neq 0$ .

- Branch if count = 0.

- Branch if condition is false.

- Branch if condition is true.

Most instructions that result in a computation (arithmetic, floating-point arithmetic, logical) include a bit that indicates whether the result of the operation should be recorded in the condition register. As will be shown, this feature is useful for branch prediction processing.

Floating-point instructions have fields for three source registers. In many cases, only two source registers are used. A few instructions involve multiplication of two source registers and then addition or subtraction of a third source register. These composite instructions are included because of the frequency of their use. For example, the inner product that is part of many matrix operations can be implemented using multiply-adds.

# 11.5 RECOMMENDED READING

The references cited in Chapter 10 are equally applicable to the material of this chapter. [BLAA97] contains a detailed discussion of instruction formats and addressing modes. In addition, the reader may wish to consult [FLYN85] for a discussion and analysis of instruction set design issues, particularly those relating to formats.

BLAA97 Blaauw, G., and Brooks, F. Computer Architecture: Concepts and Evolution. Reading, MA: Addison-Wesley, 1997.

FLYN85 Flynn, M.; Johnson, J.; and Wakefield, S. "On Instruction Sets and Their Formats." IEEE Transactions on Computers, March 1985.

# 11.6 KEY TERMS, REVIEW QUESTIONS, AND PROBLEMS

#### **Key Terms**

| autoindexing<br>base-register addressing<br>direct addressing<br>displacement addressing<br>effective address | immediate addressing indexing indirect addressing instruction format postindexing | preindexing register addressing register indirect addressing relative addressing word |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

# **Review Questions**

- 11.1 Briefly define immediate addressing.

- 11.2 Briefly define direct addressing.

- 11.3 Briefly define indirect addressing.

- 11.4 Briefly define register addressing.

- 11.5 Briefly define register indirect addressing.

- 11.6 Briefly define displacement addressing.

- 11.7 Briefly define relative addressing.

#### 412 CHAPTER 11 / INSTRUCTION SETS: ADDRESSING MODES AND FORMATS

- 11.8 What is the advantage of autoindexing?

- 11.9 What is the difference between postindexing and preindexing?

- 11.10 What facts go into determining the use of the addressing bits of an instruction?

- 11.11 What are the advantages and disadvantages of using a variable-length instruction format?

#### **Problems**

- 11.1 Given the following memory values and a one-address machine with an accumulator, what values do the following instructions load into the accumulator?

- Word 20 contains 40.

- Word 30 contains 50.

- Word 40 contains 60.

- Word 50 contains 70.

- a. LOAD IMMEDIATE 20

- b. LOAD DIRECT 20

- c. LOAD INDIRECT 20

- d. LOAD IMMEDIATE 30

- e. LOAD DIRECT 30

- f. LOAD INDIRECT 30

- 11.2 Let the address stored in the program counter be designated by the symbol X1. The instruction stored in X1 has an address part (operand reference) X2. The operand needed to execute the instruction is stored in the memory word with address X3. An index register contains the value X4. What is the relationship between these various quantities if the addressing mode of the instruction is (a) direct; (b) indirect; (c) PC relative; (d) indexed?

- 11.3 An address field in an instruction contains decimal value 14. Where is the corresponding operand located for

- a. immediate addressing?

- b. direct addressing?

- c. indirect addressing?

- d. register addressing?

- e. register indirect addressing?

- 11.4 Consider a 16-bit processor in which the following appears in main memory, starting at location 200:

| 200 | Load to AC       | Mode |

|-----|------------------|------|

| 201 | 500              |      |

| 202 | Next instruction | 1    |

The first part of the first word indicates that this instruction loads a value into an accumulator. The Mode field specifies an addressing mode and, if appropriate, indicates a source register; assume that when used, the source register is R1, which has a value of 400. There is also a base register that contains the value 100. The value of 500 in location 201 may be part of the address calculation. Assume that location 399 contains the value 999, location 400 contains the value 1000, and so on. Determine the effective address and the operand to be loaded for the following address modes:

| b. Immediate |             | <ul><li>g. Register indirect</li><li>h. Autoindexing with increment, using R1</li></ul> |

|--------------|-------------|-----------------------------------------------------------------------------------------|

| c. Indirect  | f. Register |                                                                                         |

- A PC-relative mode branch instruction is 3 bytes long. The address of the instruction, in decimal, is 256028. Determine the branch target address if the signed displacement in the instruction is -31.

- A PC-relative mode branch instruction is stored in memory at address 620<sub>10</sub>. The branch is made to location 530<sub>10</sub>. The address field in the instruction is 10 bits long. What is the binary value in the instruction?

- How many times does the processor need to refer to memory when it fetches and executes an indirect-address-mode instruction if the instruction is (a) a computation requiring a single operand; (b) a branch?

- The IBM 370 does not provide indirect addressing. Assume that the address of an operand is in main memory. How would you access the operand?

- In [COOK82], the author proposes that the PC-relative addressing modes be eliminated in favor of other modes, such as the use of a stack. What is the disadvantage of this proposal?

- 11.10 The Pentium includes the following instruction:

#### IMUL op1, op2, immediate

This instruction multiplies op2, which may be either register or memory, by the immediate operand value, and places the result in op1, which must be a register. There is no other three-operand instruction of this sort in the instruction set. What is the possible use of such an instruction? *Hint:* Consider indexing.

- Consider a processor that includes a base with indexing addressing mode. Suppose an instruction is encountered that employs this addressing mode and specifies a displacement of 1970, in decimal. Currently the base and index register contain the decimal numbers 48022 and 8, respectively. What is the address of the operand?

- Define: EA = (X)+ is the effective address equal to the contents of location X, with X incremented by one word length after the effective address is calculated; EA = -(X) is the effective address equal to the contents of location X, with X decremented by one word length before the effective address is calculated; EA = (X) is the effective address equal to the contents of location X, with X decremented by one word length after the effective address is calculated. Consider the following instructions, each in the format (Operation Source Operand, Destination Operand), with the result of the operation placed in the destination operand.

```

a. OP X_{i}(X)

```

**b.** OP (X), (X)+

c. OP(X)+,(X)

d. OP = (X), (X)

e. OP - (X), (X) +

**f.** OP (X)+, (X)+

g. OP (X) – (X)

Using X as the stack pointer, which of these instructions can pop the top two elements from the stack, perform the designated operation (e.g., ADD source to destination and store in destination), and push the result back on the stack? For each such instruction, does the stack grow toward memory location 0 or in the opposite direction?

11.13 Assume a stack-oriented processor that includes the stack operations PUSH and POP. Arithmetic operations automatically involve the top one or two stack elements. Begin with an empty stack. What stack elements remain after the following instructions are executed?

PUSH 4

PUSH 7

PUSH 8

ADD

PUSH 10

**SUB**

**MUL**

#### 414 CHAPTER 11 / INSTRUCTION SETS: ADDRESSING MODES AND FORMATS

- 11.14 Justify the assertion that a 32-bit instruction is probably much less than twice as useful as a 16-bit instruction.

- 11.15 Why was IBM's decision to move from 36 bits to 32 bits per word wrenching, and to whom?

- **11.16** Assume an instruction set that uses a fixed 16-bit instruction length. Operand specifiers are 6 bits in length. There are *K* two-operand instructions and *L* zero-operand instructions. What is the maximum number of one-operand instructions that can be supported?

- 11.17 Design a variable-length opcode to allow all of the following to be encoded in a 36-bit instruction:

- instructions with two 15-bit addresses and one 3-bit register number

- instructions with one 15-bit address and one 3-bit register number

- instructions with no addresses or registers

- 11.18 Consider the results of Problem 10.6. Assume that M is a 16-bit memory address and that X, Y, and Z are either 16-bit addresses or 4-bit register numbers. The one-address machine uses an accumulator, and the two- and three-address machines have 16 registers and instructions operating on all combinations of memory locations and registers. Assuming 8-bit opcodes and instruction lengths that are multiples of 4 bits, how many bits does each machine need to compute X?

- 11.19 Is there any possible justification for an instruction with two opcodes?

- 11.20 The 16-bit Zilog Z8001 has the following general instruction format:

|     |      |            |                                         |       |   |              |    |   |   |       |      | <br>   |       |   |

|-----|------|------------|-----------------------------------------|-------|---|--------------|----|---|---|-------|------|--------|-------|---|

| l M | lode | i di Karaj | . 12 - 12 - 12 - 12 - 12 - 12 - 12 - 12 | Opcod | e | e con e sa e | w/ | b | C | perar | id 2 | <br>Ор | erand | 1 |

The *mode* field specifies how to locate the operands from the *operand* fields. The *w/b* field is used in certain instructions to specify whether the operands are bytes or 16-bit words. The *operand 1* field may (depending on the *mode field* contents) specify one of 16 general-purpose registers. The *operand 2* field may specify any general-purpose registers except register 0. When the *operand 2* field is all zeros, each of the original opcodes takes on a new meaning.

- a. How many opcodes are provided on the Z8001?

- **b.** Suggest an efficient way to provide more opcodes and indicate the trade-off involved.

all the contractions (marketic processes)

yri rysk dra dalantaru brahandella bushqadis restit

ado reservido pelho especificado altro belante en properto de la freciona

# PROCESSOR STRUCTURE AND FUNCTION

- 12.1 Processor Organization

- 12.2 Register Organization

- 12.3 Instruction Cycle

- 12.4 Instruction Pipelining

- 12.5 The Pentium Processor

- 12.6 The PowerPC Processor

- 12.7 Recommended Reading

- 12.8 Key Terms, Review Questions, and Problems

#### **KEY POINTS**

- A processor includes both user-visible registers and control/status registers. The former may be referenced, implicitly or explicitly, in machine instructions. User-visible registers may be general purpose or have a special use, such as fixed-point or floating-point numbers, addresses, indexes, and segment pointers. Control and status registers are used to control the operation of the processor. One obvious example is the program counter. Another important example is a program status word (PSW) that contains a variety of status and condition bits. These include bits to reflect the result of the most recent arithmetic operation, interrupt enable bits, and an indicator of whether the processor is executing in supervisor or user mode.

- Processors make use of instruction pipelining to speed up execution. In essence, pipelining involves breaking up the instruction cycle into a number of separate stages that occur in sequence, such as fetch instruction, decode instruction, determine operand addresses, fetch operands, execute instruction, and write operand result. Instructions move through these stages, as on an assembly line, so that in principle, each stage can be working on a different instruction at the same time. The occurrence of branches and dependencies between instructions complicates the design and use of pipelines.

This chapter discusses aspects of the processor not yet covered in Part Three and sets the stage for the discussion of RISC and superscalar architecture in Chapters 13 and 14.

We begin with a summary of processor organization. Registers, which form the internal memory of the processor, are then analyzed. We are then in a position to return to the discussion (begun in Section 3.2) of the instruction cycle. A description of the instruction cycle and a common technique known as instruction pipelining complete our description. The chapter concludes with an examination of some additional aspects of the Pentium and PowerPC organizations.

# 12.1 PROCESSOR ORGANIZATION

To understand the organization of the processor, let us consider the requirements placed on the processor, the things that it must do:

- Fetch instruction: The processor reads an instruction from memory (register, cache, main memory).

- Interpret instruction: The instruction is decoded to determine what action is required.

- Fetch data: The execution of an instruction may require reading data from memory or an I/O module.

- Process data: The execution of an instruction may require performing some arithmetic or logical operation on data.

- Write data: The results of an execution may require writing data to memory or an I/O module.

To do these things, it should be clear that the processor needs to store some data temporarily. It must remember the location of the last instruction so that it can know where to get the next instruction. It needs to store instructions and data temporarily while an instruction is being executed. In other words, the processor needs a small internal memory.

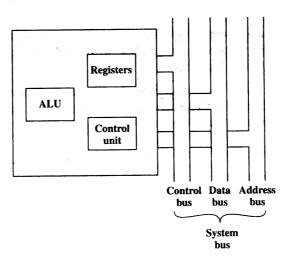

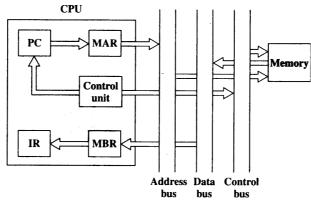

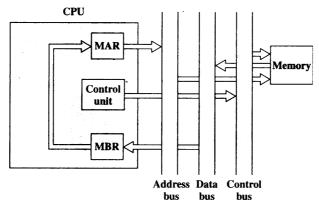

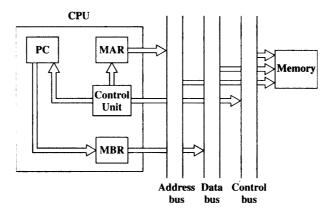

Figure 12.1 is a simplified view of a processor, indicating its connection to the rest of the system via the system bus. A similar interface would be needed for any of the interconnection structures described in Chapter 3. The reader will recall that the major components of the processor are an arithmetic and logic unit (ALU) and a control unit (CU). The ALU does the actual computation or processing of data. The control unit controls the movement of data and instructions into and out of the processor and controls the operation of the ALU. In addition, the figure shows a minimal internal memory, consisting of a set of storage locations, called registers.

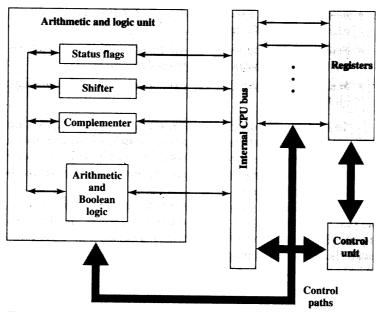

Figure 12.2 is a slightly more detailed view of the processor. The data transfer and logic control paths are indicated, including an element labeled internal processor bus. This element is needed to transfer data between the various registers and the ALU because the ALU in fact operates only on data in the internal processor memory. The figure also shows typical basic elements of the ALU. Note the similarity between the internal structure of the computer as a whole and the internal structure of the processor. In both cases, there is a small collection of major elements (computer: processor, I/O, memory; processor: control unit, ALU, registers) connected by data paths.

Figure 12.1 The CPU with the System Bus

Figure 12.2 Internal Structure of the CPU

# 12.2 REGISTER ORGANIZATION

As we discussed in Chapter 4, a computer system employs a memory hierarchy. At higher levels of the hierarchy, memory is faster, smaller, and more expensive (per bit). Within the processor, there is a set of registers that function as a level of memory above main memory and cache in the hierarchy. The registers in the processor perform two roles:

- User-visible registers: Enable the machine- or assembly language programmer to minimize main memory references by optimizing use of registers.

- Control and status registers: Used by the control unit to control the operation of the processor and by privileged, operating system programs to control the execution of programs.

There is not a clean separation of registers into these two categories. For example, on some machines the program counter is user visible (e.g., Pentium), but on many it is not. For purposes of the following discussion, however, we will use these categories.

## User-Visible Registers

A user-visible register is one that may be referenced by means of the machine language that the processor executes. We can characterize these in the following categories:

- General purpose

- Data

- Address

- · Condition codes

General-purpose registers can be assigned to a variety of functions by the programmer. Sometimes their use within the instruction set is orthogonal to the operation. That is, any general-purpose register can contain the operand for any opcode. This provides true general-purpose register use. Often, however, there are restrictions. For example, there may be dedicated registers for floating-point and stack operations.

In some cases, general-purpose registers can be used for addressing functions (e.g., register indirect, displacement). In other cases, there is a partial or clean separation between data registers and address registers. Data registers may be used only to hold data and cannot be employed in the calculation of an operand address. Address registers may themselves be somewhat general purpose, or they may be devoted to a particular addressing mode. Examples include the following:

- Segment pointers: In a machine with segmented addressing (see Section 8.3), a segment register holds the address of the base of the segment. There may be multiple registers: for example, one for the operating system and one for the current process.

- Index registers: These are used for indexed addressing and may be autoindexed.

- Stack pointer: If there is user-visible stack addressing, then typically there is a dedicated register that points to the top of the stack. This allows implicit addressing; that is, push, pop, and other stack instructions need not contain an explicit stack operand.

There are several design issues to be addressed here. An important issue is whether to use completely general-purpose registers or to specialize their use. We have already touched on this issue in the preceding chapter because it affects instruction set design. With the use of specialized registers, it can generally be implicit in the opcode which type of register a certain operand specifier refers to. The operand specifier must only identify one of a set of specialized registers rather than one out of all the registers, thus saving bits. On the other hand, this specialization limits the programmer's flexibility.

Another design issue is the number of registers, either general purpose or data plus address, to be provided. Again, this affects instruction set design because more registers require more operand specifier bits. As we previously discussed, somewhere between 8 and 32 registers appears optimum [LUND77]. Fewer registers result in more memory references; more registers do not noticeably reduce memory references (e.g., see [WILL90]). However, a new approach, which finds advantage in the use of hundreds of registers, is exhibited in some RISC systems and is discussed in Chapter 13.

Finally, there is the issue of register length. Registers that must hold addresses obviously must be at least long enough to hold the largest address. Data registers should be able to hold values of most data types. Some machines allow two contiguous registers to be used as one for holding double-length values.

A final category of registers, which is at least partially visible to the user, holds condition codes (also referred to as flags). Condition codes are bits set by the processor hardware as the result of operations. For example, an arithmetic operation may

Table 12.1 Condition Codes

#### from the state of **Disadvantages** 1. Because condition codes are set by normal 1. Condition codes add complexity, both to the arithmetic and data movement instructions, hardware and software. Condition code bits are they should reduce the number of COMPARE often modified in different ways by different and TEST instructions needed. instructions, making life more difficult for both the 2. Conditional instructions, such as BRANCH microprogrammer and compiler writer. are simplified relative to composite instructions, 2. Condition codes are irregular; they are typically soci in TEST AND BRANCH. not part of the main data path, so they require extra hardware connections. 3. Condition codes facilitate multiway branches. For example, a TEST instruction can be followed 3. Often condition code machines must add special by two branches, one on less than or equal to zero non-condition-code instructions for special and one on greater than zero. situations anyway, such as bit checking, loop control, and atomic semaphore operations. 4. In a pipelined implementation, condition codes S. Andrew Market of the program of the control of the require special synchronization to avoid conflicts.

produce a positive, negative, zero, or overflow result. In addition to the result itself being stored in a register or memory, a condition code is also set. The code may subsequently be tested as part of a conditional branch operation.

Condition code bits are collected into one or more registers. Usually, they form part of a control register. Generally, machine instructions allow these bits to be read by implicit reference, but the programmer cannot alter them.

Many processors, including those based on the IA-64 architecture and the MIPS processors, do not use condition codes at all. Rather, conditional branch instructions specify a comparison to be made and act on the result of the comparison, without storing a condition code. Table 12.1, based on [DERO87], lists key advantages and disadvantages of condition codes.

In some machines, a subroutine call will result in the automatic saving of all user-visible registers, to be restored on return. The processor performs the saving and restoring as part of the execution of call and return instructions. This allows each subroutine to use the user-visible registers independently. On other machines, it is the responsibility of the programmer to save the contents of the relevant user-visible registers prior to a subroutine call, by including instructions for this purpose in the program.

#### Control and Status Registers

There are a variety of processor registers that are employed to control the operation of the processor. Most of these, on most machines, are not visible to the user. Some of them may be visible to machine instructions executed in a control or operating system mode.

Of course, different machines will have different register organizations and use different terminology. We list here a reasonably complete list of register types, with a brief description.

Four registers are essential to instruction execution:

- Program counter (PC): Contains the address of an instruction to be fetched

- Instruction register (IR): Contains the instruction most recently fetched

- Memory address register (MAR): Contains the address of a location in memory

- Memory buffer register (MBR): Contains a word of data to be written to memory or the word most recently read

Not all processors have internal registers designated as MAR and MBR, but some equivalent buffering mechanism is needed whereby the bits to be transferred to the system bus are staged and the bits to be read from the data bus are temporarily

Typically, the processor updates the PC after each instruction fetch so that the PC always points to the next instruction to be executed. A branch or skip instruction will also modify the contents of the PC. The fetched instruction is loaded into an IR, where the opcode and operand specifiers are analyzed. Data are exchanged with memory using the MAR and MBR. In a bus-organized system, the MAR connects directly to the address bus, and the MBR connects directly to the data bus. User-visible registers, in turn, exchange data with the MBR.

The four registers just mentioned are used for the movement of data between the processor and memory. Within the processor, data must be presented to the ALU for processing. The ALU may have direct access to the MBR and user-visible registers. Alternatively, there may be additional buffering registers at the boundary to the ALU; these registers serve as input and output registers for the ALU and exchange data with the MBR and user-visible registers.

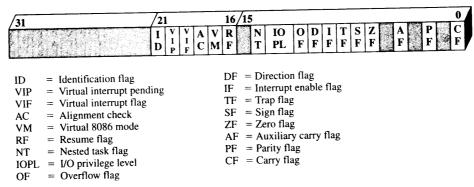

Many processor designs include a register or set of registers, often known as the program status word (PSW), that contain status information. The PSW typically contains condition codes plus other status information. Common fields or flags include the following:

- Sign: Contains the sign bit of the result of the last arithmetic operation.

- **Zero:** Set when the result is 0.

- Carry: Set if an operation resulted in a carry (addition) into or borrow (subtraction) out of a high-order bit. Used for multiword arithmetic operations.

- Equal: Set if a logical compare result is equality.

- Overflow: Used to indicate arithmetic overflow.

- Interrupt enable/disable: Used to enable or disable interrupts.

- Supervisor: Indicates whether the processor is executing in supervisor or user mode. Certain privileged instructions can be executed only in supervisor mode, and certain areas of memory can be accessed only in supervisor mode.

A number of other registers related to status and control might be found in a particular processor design. There may be a pointer to a block of memory containing additional status information (e.g., process control blocks). In machines using vectored interrupts, an interrupt vector register may be provided. If a stack is used to implement certain functions (e.g., subroutine call), then a system stack pointer is needed. A page table pointer is used with a virtual memory system. Finally, registers may be used in the control of I/O operations.

A number of factors go into the design of the control and status register organization. One key issue is operating system support. Certain types of control information are of specific utility to the operating system. If the processor designer has a functional understanding of the operating system to be used, then the register organization can to some extent be tailored to the operating system.

Another key design decision is the allocation of control information between registers and memory. It is common to dedicate the first (lowest) few hundred or thousand words of memory for control purposes. The designer must decide how much control information should be in registers and how much in memory. The usual trade-off of cost versus speed arises.

# **Example Microprocessor Register Organizations**

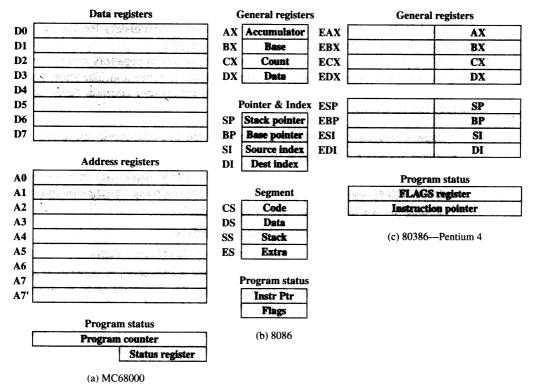

It is instructive to examine and compare the register organization of comparable systems. In this section, we look at two 16-bit microprocessors that were designed at about the same time: the Motorola MC68000 [STRI79] and the Intel 8086 [MORS78]. Figures 12.3a and b depict the register organization of each; purely internal registers, such as a memory address register, are not shown.

Figure 12.3 Example Microprocessor Register Organizations

The MC68000 partitions its 32-bit registers into eight data registers and nine address registers. The eight data registers are used primarily for data manipulation and are also used in addressing as index registers. The width of the registers allows 8-, 16-, and 32-bit data operations, determined by opcode. The address registers contain 32-bit (no segmentation) addresses; two of these registers are also used as stack pointers, one for users and one for the operating system, depending on the current execution mode. Both registers are numbered 7, because only one can be used at a time. The MC68000 also includes a 32-bit program counter and a 16-bit status register.

The Motorola team wanted a very regular instruction set, with no specialpurpose registers. A concern for code efficiency led them to divide the registers into two functional components, saving one bit on each register specifier. This seems a reasonable compromise between complete generality and code compaction.

The Intel 8086 takes a different approach to register organization. Every register is special purpose, although some registers are also usable as general purpose. The 8086 contains four 16-bit data registers that are addressable on a byte or 16-bit basis, and four 16-bit pointer and index registers. The data registers can be used as general purpose in some instructions. In others, the registers are used implicitly. For example, a multiply instruction always uses the accumulator. The four pointer registers are also used implicitly in a number of operations; each contains a segment offset. There are also four 16-bit segment registers. Three of the four segment registers are used in a dedicated, implicit fashion, to point to the segment of the current instruction (useful for branch instructions), a segment containing data, and a segment containing a stack, respectively. These dedicated and implicit uses provide for compact encoding at the cost of reduced flexibility. The 8086 also includes an instruction pointer and a set of 1-bit status and control flags.

The point of this comparison should be clear. There is no universally accepted philosophy concerning the best way to organize processor registers [TOON81]. As with overall instruction set design and so many other processor design issues, it is still a matter of judgment and taste.

A second instructive point concerning register organization design is illustrated in Figure 12.3c. This figure shows the user-visible register organization for the Intel 80386 [ELAY85], which is a 32-bit microprocessor designed as an extension of the 8086.1 The 80386 uses 32-bit registers. However, to provide upward compatibility for programs written on the earlier machine, the 80386 retains the original register organization embedded in the new organization. Given this design constraint, the architects of the 32-bit processors had limited flexibility in designing the register organization.

# 12.3 INSTRUCTION CYCLE

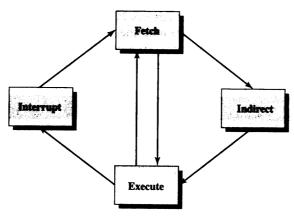

In Section 3.2, we described the processor's instruction cycle (Figure 3.9). To recall, an instruction cycle includes the following subcycles:

Because the MC68000 already uses 32-bit registers, the MC68020 [MACG84], which is a full 32-bit architecture, uses the same register organization.

- Fetch: Read the next instruction from memory into the processor.

- Execute: Interpret the opcode and perform the indicated operation.

- Interrupt: If interrupts are enabled and an interrupt has occurred, save the current process state and service the interrupt.

We are now in a position to elaborate somewhat on the instruction cycle. First, we must introduce one additional subcycle, known as the indirect cycle.

#### The Indirect Cycle

We have seen, in Chapter 11, that the execution of an instruction may involve one or more operands in memory, each of which requires a memory access. Further, if indirect addressing is used, then additional memory accesses are required.

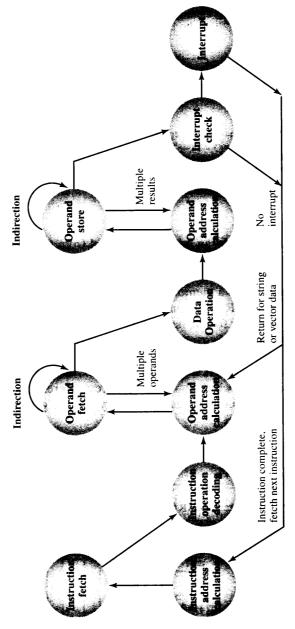

We can think of the fetching of indirect addresses as one more instruction subcycle. The result is shown in Figure 12.4. The main line of activity consists of alternating instruction fetch and instruction execution activities. After an instruction is fetched, it is examined to determine if any indirect addressing is involved. If so, the required operands are fetched using indirect addressing. Following execution, an interrupt may be processed before the next instruction fetch.

Another way to view this process is shown in Figure 12.5, which is a revised version of Figure 3.12. This illustrates more correctly the nature of the instruction cycle. Once an instruction is fetched, its operand specifiers must be identified. Each input operand in memory is then fetched, and this process may require indirect addressing. Register-based operands need not be fetched. Once the opcode is executed, a similar process may be needed to store the result in main memory.

#### **Data Flow**

The exact sequence of events during an instruction cycle depends on the design of the processor. We can, however, indicate in general terms what must happen. Let us assume that a processor that employs a memory address register (MAR), a memory buffer register (MBR), a program counter (PC), and an instruction register (IR).

Figure 12.4 The Instruction Cycle

Figure 12.5 Instruction Cycle State Diagram

MBR = Memory buffer register MAR = Memory address register

IR = Instruction register

PC = Program counter

Figure 12.6 Data Flow, Fetch Cycle

During the fetch cycle, an instruction is read from memory. Figure 12.6 shows the flow of data during this cycle. The PC contains the address of the next instruction to be fetched. This address is moved to the MAR and placed on the address bus. The control unit requests a memory read, and the result is placed on the data bus and copied into the MBR and then moved to the IR. Meanwhile, the PC is incremented by 1, preparatory for the next fetch.

Once the fetch cycle is over, the control unit examines the contents of the IR to determine if it contains an operand specifier using indirect addressing. If so, an indirect cycle is performed. As shown in Figure 12.7, this is a simple cycle. The rightmost N bits of the MBR, which contain the address reference, are transferred to the MAR. Then the control unit requests a memory read, to get the desired address of the operand into the MBR.

Figure 12.7 Data Flow, Indirect Cycle

Figure 12.8 Data Flow, Interrupt Cycle

The fetch and indirect cycles are simple and predictable. The execute cycle takes many forms; the form depends on which of the various machine instructions is in the IR. This cycle may involve transferring data among registers, read or write from memory or I/O, and/or the invocation of the ALU.

Like the fetch and indirect cycles, the interrupt cycle is simple and predictable (Figure 12.8). The current contents of the PC must be saved so that the processor can resume normal activity after the interrupt. Thus, the contents of the PC are transferred to the MBR to be written into memory. The special memory location reserved for this purpose is loaded into the MAR from the control unit. It might, for example, be a stack pointer. The PC is loaded with the address of the interrupt routine. As a result, the next instruction cycle will begin by fetching the appropriate instruction.

#### 12.4 INSTRUCTION PIPELINING

As computer systems evolve, greater performance can be achieved by taking advantage of improvements in technology, such as faster circuitry. In addition, organizational enhancements to the processor can improve performance. We have already seen some examples of this, such as the use of multiple registers rather than a single accumulator, and the use of a cache memory. Another organizational approach, which is quite common, is instruction pipelining.

#### **Pipelining Strategy**

Instruction pipelining is similar to the use of an assembly line in a manufacturing plant. An assembly line takes advantage of the fact that a product goes through various stages of production. By laying the production process out in an assembly line, products at various stages can be worked on simultaneously. This process is also referred to as pipelining, because, as in a pipeline, new inputs are accepted at one end before previously accepted inputs appear as outputs at the other end.

To apply this concept to instruction execution, we must recognize that, in fact, an instruction has a number of stages. Figure 12.5, for example, breaks the

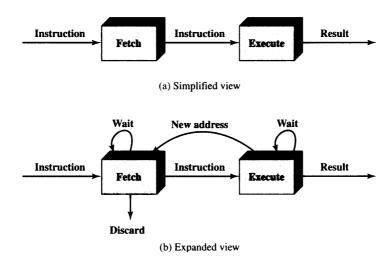

Figure 12.9 Two-Stage Instruction Pipeline

instruction cycle up into 10 tasks, which occur in sequence. Clearly, there should be some opportunity for pipelining.

As a simple approach, consider subdividing instruction processing into two stages: fetch instruction and execute instruction. There are times during the execution of an instruction when main memory is not being accessed. This time could be used to fetch the next instruction in parallel with the execution of the current one. Figure 12.9a depicts this approach. The pipeline has two independent stages. The first stage fetches an instruction and buffers it. When the second stage is free, the first stage passes it the buffered instruction. While the second stage is executing the instruction, the first stage takes advantage of any unused memory cycles to fetch and buffer the next instruction. This is called instruction prefetch or fetch overlap.

It should be clear that this process will speed up instruction execution. If the fetch and execute stages were of equal duration, the instruction cycle time would be halved. However, if we look more closely at this pipeline (Figure 12.9b), we will see that this doubling of execution rate is unlikely for two reasons:

- 1. The execution time will generally be longer than the fetch time. Execution will involve reading and storing operands and the performance of some operation. Thus, the fetch stage may have to wait for some time before it can empty its buffer.

- 2. A conditional branch instruction makes the address of the next instruction to be fetched unknown. Thus, the fetch stage must wait until it receives the next instruction address from the execute stage. The execute stage may then have to wait while the next instruction is fetched.

Guessing can reduce the time loss from the second reason. A simple rule is the following: When a conditional branch instruction is passed on from the fetch to the execute stage, the fetch stage fetches the next instruction in memory after the branch instruction. Then, if the branch is not taken, no time is lost. If the branch is taken, the fetched instruction must be discarded and a new instruction fetched.

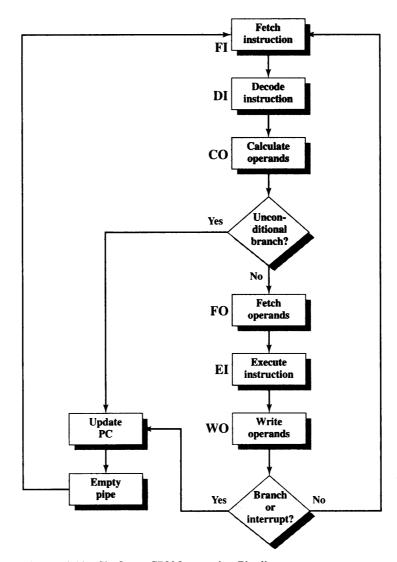

While these factors reduce the potential effectiveness of the two-stage pipeline, some speedup occurs. To gain further speedup, the pipeline must have more stages. Let us consider the following decomposition of the instruction processing.

- Fetch instruction (FI): Read the next expected instruction into a buffer.

- Decode instruction (DI): Determine the opcode and the operand specifiers.

- Calculate operands (CO): Calculate the effective address of each source operand. This may involve displacement, register indirect, indirect, or other forms of address calculation.

- Fetch operands (FO): Fetch each operand from memory. Operands in registers need not be fetched.

- Execute instruction (EI): Perform the indicated operation and store the result, if any, in the specified destination operand location.

- Write operand (WO): Store the result in memory.

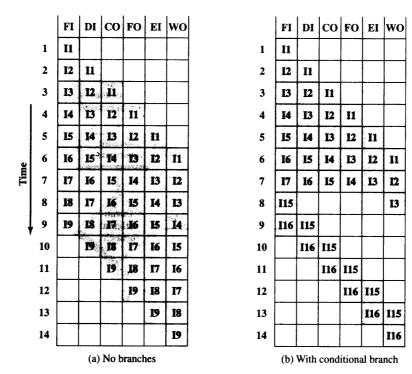

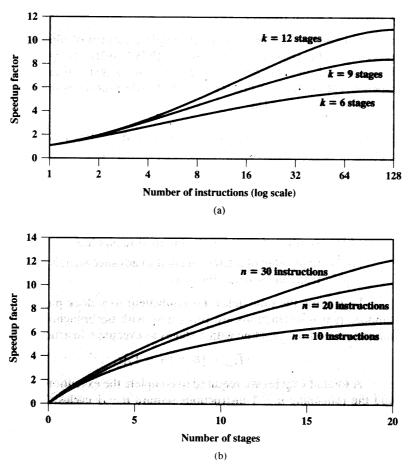

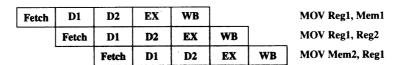

With this decomposition, the various stages will be of more nearly equal duration. For the sake of illustration, let us assume equal duration. Using this assumption, Figure 12.10 shows that a six-stage pipeline can reduce the execution time for 9 instructions from 54 time units to 14 time units.

Several comments are in order: The diagram assumes that each instruction goes through all six stages of the pipeline. This will not always be the case. For example, a load instruction does not need the WO stage. However, to simplify the pipeline hardware, the timing is set up assuming that each instruction requires all six stages. Also, the diagram assumes that all of the stages can be performed in parallel. In particular, it is assumed that there are no memory conflicts. For example, the FI, FO, and WO stages involve a memory access. The diagram implies that all these accesses can

|               |    |    | Tim | e  | <b>→</b> |    |    |    |    |    |    |    |    |    |

|---------------|----|----|-----|----|----------|----|----|----|----|----|----|----|----|----|

|               | 1  | 2  | 3   | 4  | 5        | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

| Instruction 1 | FI | DI | со  | FO | EI       | wo |    |    |    |    |    |    |    |    |

| Instruction 2 |    | FI | DI  | со | FO       | EI | wo |    |    |    |    |    |    |    |

| Instruction 3 |    |    | FI  | DI | со       | FO | EI | wo |    |    |    |    |    |    |

| Instruction 4 |    |    |     | FI | DI       | СО | FO | EI | wo |    |    |    |    |    |

| Instruction 5 |    |    |     |    | FI       | DI | со | FO | EI | wo |    |    |    |    |

| Instruction 6 |    |    |     |    |          | FI | DI | со | FO | EI | wo |    |    |    |

| Instruction 7 |    |    |     |    |          |    | FI | DI | со | FO | EI | wo |    |    |

| Instruction 8 |    |    |     |    |          |    |    | FI | DI | со | FO | EI | wo |    |

| Instruction 9 |    |    |     |    |          |    |    |    | FI | DI | со | FO | EI | wo |

Figure 12.10 Timing Diagram for Instruction Pipeline Operation

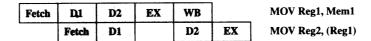

|                | Time |    |    |    |    |    |    | Branch penalty |    |    |    |    |    |    |  |

|----------------|------|----|----|----|----|----|----|----------------|----|----|----|----|----|----|--|

|                | 1    | 2  | 3  | 4  | 5  | 6  | 7  | 8              | 9  | 10 | 11 | 12 | 13 | 14 |  |

| Instruction 1  | FI   | DI | со | FO | EI | wo |    |                |    |    |    |    |    |    |  |

| Instruction 2  |      | FI | DI | со | FO | EI | wo |                |    |    |    |    |    |    |  |

| Instruction 3  |      |    | FI | DI | со | FO | EI | wo             |    |    |    |    |    |    |  |

| Instruction 4  |      |    |    | FI | DI | со | FO |                |    |    |    |    |    |    |  |

| Instruction 5  |      |    |    |    | FI | DI | со |                |    |    |    |    |    |    |  |